こんにちは。レスター エンベデッド技術本部です。

今回は「ASICの歩留まり」に関するテーマをベースに、歩留まりの考え方や原因、向上技術までをわかりやすく整理してみます。

歩留まりとは?

半導体の「歩留まり」とは良品(規格を満たしている)の割合を指しており%で表現されます。

歩留まりに影響する要素としては、工場の品質(装置、クリーンルームや、製造技術(プロセス、テスト、パッケージ 各技術)など)と微細化による難易向上があげられます。

特にASICのようなカスタムLSIでは、量産後に不良が発生すると大きな損失になるため、歩留まりの高さは極めて重要です。

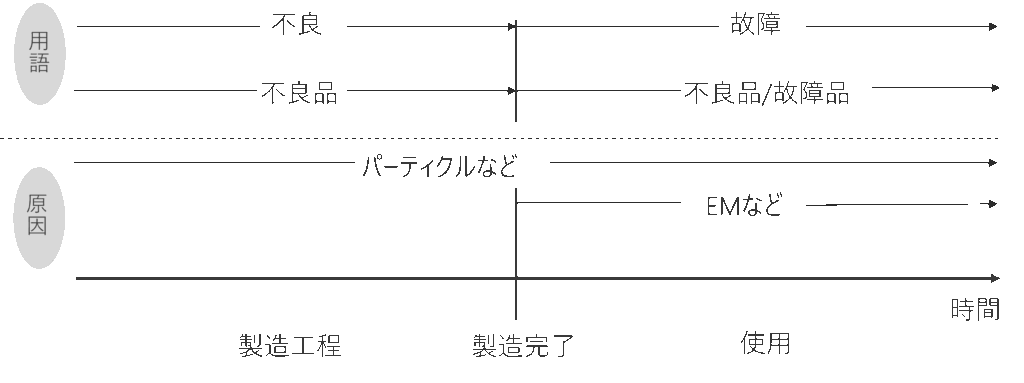

LSIの「不良」と「故障」の違い

- 不良:製造段階で発見される“問題”を指しています。(初期不良 などと言われています)

- 故障:使用段階で発見される“問題”を指しています。(経年劣化・環境要因による故障 などと言われています。)

この違いを理解することが、歩留まり改善や信頼性評価において重要なポイントです。

市場をリードするファウンドリー企業

現在、微細化技術においてリーダーシップを握るのは以下の3社です:

| ファウンドリー | 主な特徴 |

|---|---|

| TSMC | 業界最大手。顧客との協業を重視し、3nmプロセスではAppleなどが主要顧客に。GAAFETは採用しておらずFinFETを維持。 |

| Samsung | 先進的な技術導入が早く、3nm世代で世界初のGAAFET(MBCFET™)を採用。量産時期の早さに強み。 |

| UMC | 熟成したプロセスに特化しており、アナログ系の用途に適していると言えます。また、Intelと提携してプロセス開発も実施中。 |

これらのファウンドリーはそれぞれ異なる戦略・品質への取組みにより微細化を進めております。

故障分類と工程との関係

ここでは、チップ部とパッケージ部に分けて、代表的な不良/故障とその工程の関係性を表にまとめました。

チップ製造工程における故障原因

| 工程/部位と処理内容 | 故障例 |

|---|---|

| Si基板/ゲート絶縁膜⇒イオン注入・酸化・成膜 | BTI、TDDB、HCI、結晶欠陥、ホットキャリア注入、NBTI など |

| 配線部⇒配線形成・エッチング・CMP | 配線オープン、金属残渣、エレクトロマイグレーション(EM)、応力ずれ、段部断線 など |

| パシベーション部⇒絶縁膜形成・表面保護 | 表面汚染、吸湿、クラック、表面チャージ層の形成 など |

パッケージング工程における故障原因

| 工程 | 故障例 |

|---|---|

| ダイボンディング | チップ位置ズレ、接着不良、熱ストレス破損 |

| ワイヤボンディング | ボンディング不良、ワイヤ断線 |

| パッケージ成形 | クラック、樹脂剥離 |

| 実装工程 | はんだ割れ、空乏層剥離、フラックス残渣 |

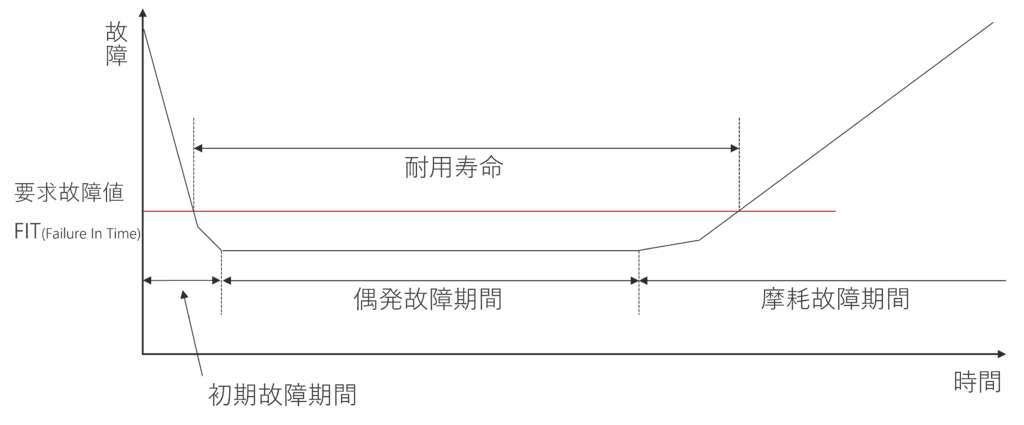

バスタブカーブの見方

バスタブカーブは、信頼性、製品寿命分析に使われる概念で、バスタブの形状に似ている事から名付けられています。

故障率を時間の経過とともに現わしており、初期故障期間、偶発故障期間、摩耗故障期間に分類されています。

- 初期:製造由来の不良で故障率が高い

- 中期:偶発故障が少なく安定

- 後期:経年劣化で故障率が上昇

→ 故障率を考える際に、対象物の発生要因を考察を補助する概念となります。

歩留まりを支える「冗長救済」技術

半導体設計において、メモリセルや回路故障をある程度想定して、“予備の回路”や“予備のセル”を準備しておき、故障発生時にそれらを機能させて現状を維持する技術を“ 冗長技術”と言います。

例えば、メモリセルの場合の参考技法は以下となります。

- MBIST(Memory Built-in Self Test):内蔵セルによる自己診断

- BISR(Built-In Self Repair):自動冗長切替

- eFUSE:物理的な予備回路の切り替え(ヒューズを飛ばす)

冗長救済可能な不良とは?

冗長救済可能なのは「局所的な故障」

| 故障範囲 | 冗長救済可否 | 備考 |

|---|---|---|

| 1bit不良 | 〇 | 冗長セルと置換可能 |

| 1Row不良 | △ | セル設計次第で可能 |

| 全領域不良 | ✕ | 冗長領域が足りない |

→ 実際の統計では、全不良の40%程度が救済できるというケースもあります。

チップレットという選択肢

最近注目されるのが「チップレット」技術。

従来の“全ての機能を1Chip搭載”ではなく、複数のチップに分けてパッケージングする選択です。

| メリット | デメリット |

|---|---|

| 1箇所の不具合による全体破棄を避けるため、あらかじめ分割しておくことで、問題のないチップはそのまま利用可能 | 信号遅延や消費電力増加など性能低下が懸念される |

| 各チップを先端テク、成熟テクで作り分ける事により歩留まりの改善が期待できる | 設計・検証がより複雑に |

この技法は、歩留まりと開発&製造コストを見極める事により有効性を判断する必要が有ります。

まとめ

- ファウンダリーに求められる質・供給能力としても歩留りは重要

- ASICに搭載されるメモリ(容量)も増えてきており、SRAM冗長救済は高い効果を発揮する

- 今後も更に微細化・高集積化されるASICにおいてもチップレットの手法を使えば歩留りに対する効果は期待大

注)冗長救済/チップレットともにメリットとデメリットのトレードオフが存在するため、適用にあたっては考慮が必要な技術(手法)

関連製品

- Socionext

- PGC

参考文献

- Samsung

- TSMC

- Intel

更新履歴

2025/09/19 新規作成