こんにちは。レスター エンベデッド技術本部です。

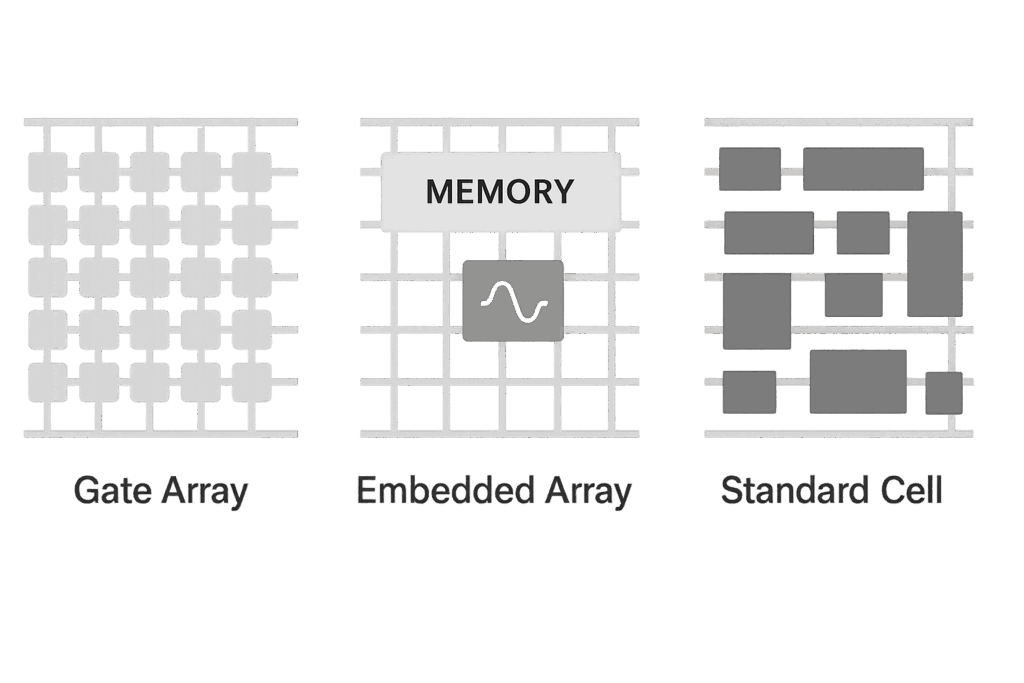

今回は「ASICの構造」について、特に「Gate Array」「Embedded Array」「Standard Cell」という3つの構成方式の違いに焦点を当てて

解説します。

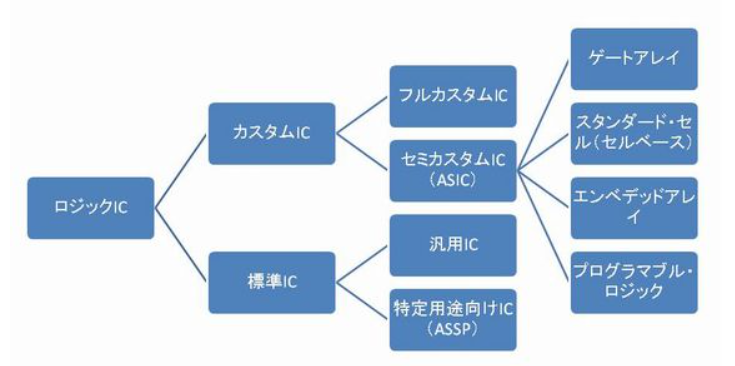

ASICにも「構造の種類」がある?

EDN JAPAN「第8回 FPGAとカスタムLSI:デジタルIC 基礎の基礎 – EDN Japan」より参照

ASIC(Application Specific Integrated Circuit)というと、“特定用途向けの専用LSI”という印象が強いかと思いますが、

実はその中でも構造によって設計やコスト、自由度に大きな差があります。

本記事では、ASIC構造の代表例である以下の3方式を取り上げて比較していきます。

- Gate Array(ゲートアレイ)

- Embedded Array(エンベデッドアレイ)

- Standard Cell(スタンダードセル)

Gate Array(ゲートアレイ)とは?

Gate Arrayは、あらかじめ用意されたトランジスタアレイ(下地)を使い、上層の配線だけをカスタムすることでロジックを構成する手法です。

特徴として、

- ベーシックセル(基本トランジスタ構造)が規則正しく並ぶ

- 配線層のみカスタム → 短納期・低コスト

- 回路の自由度は低く、無駄な領域が発生しやすい

という形式になっています。

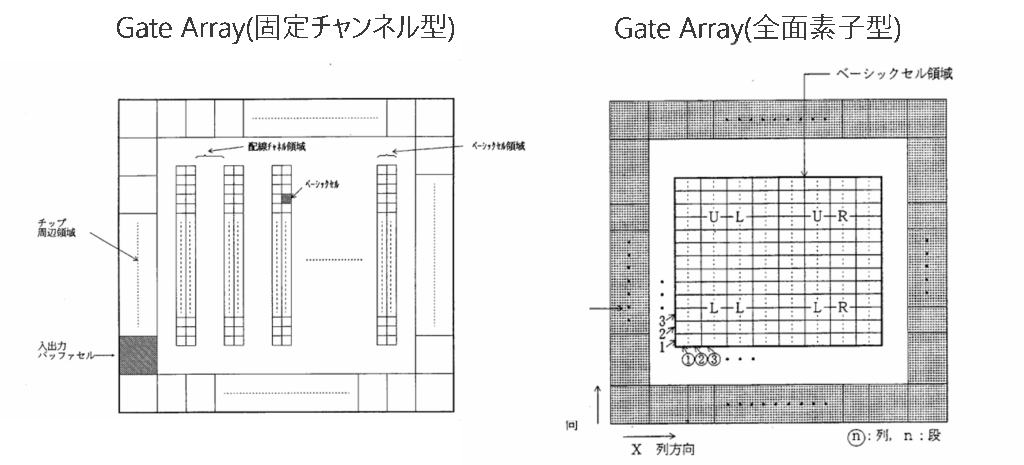

2つのバリエーション

Gate Arrayには主に以下の2タイプがあります

- Gate Array(固定チャンネル型):配線用のチャネルが明示的に設けられている。初期のGate Arrayで使用。

- Gate Array(全面素子型):配線チャネルをなくし、ベーシックセルを密に配置して高密度化

どちらもベーシックセル+入出力バッファで構成され、現在は全面素子型が主流です。

1⃣ Gate Array(固定チャンネル型)

この方式では、配線チャネル領域が明確に存在しており、構造上は以下の3層で構成されます。

- チップ周辺領域 :外部デバイスとのインターフェース用バッファ配置

- ベーシックセル領域:論理回路を構成するセルが規則的に配置

- 配線チャネル領域 :金属配線による接続パスが確保された領域

設計ツールでの扱いやすさが高く、古くから使われてきた構造です。

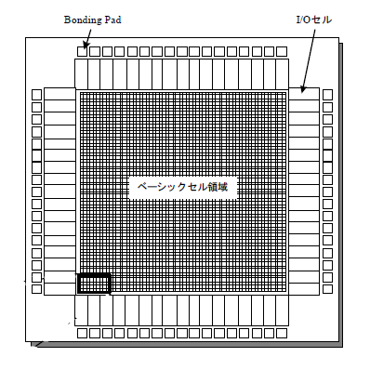

2⃣Gate Array(全面素子型)

こちらは配線チャネルを排除し、ベーシックセルをチップ全体に敷き詰めた構造です。

- 高集積・高密度が可能

- 配置の自由度は高まるが、配線設計の難易度は若干上がる

ベーシックセルとセルの構成

ベーシックセル自体には論理機能はなく、Pチャネル/Nチャネルトランジスタが含まれるのみ。

それを金属配線で結線して論理ブロック(セル)に仕立てることで、NAND、NOR、カウンタなどの機能を持たせます。

→ 配線を変えるだけで様々なロジックを実現できるのが特徴です。

Gate Array方式のメリット・デメリット

- メリット:配線のみの設計で済むため、開発期間が短く、製造コストも低い

- デメリット:回路の自由度が低く、集積度や性能に限界がある

また、パッケージや試験基板などを共通化できる点もコストメリットの一因です。

Embedded Array(エンベデッドアレイ)とは?

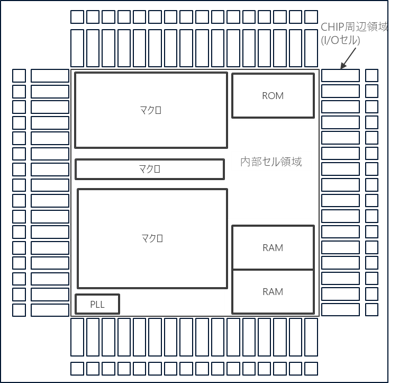

Embedded Arrayは、全面素子型Gate Arrayの構造の一部にマクロIP(例:RAM、PLLなど)を埋め込んだ構造です。

- 一部をベーシックセルから切り離すことで、より複雑な機能の実装が可能

- ただし、共通の下地が使えなくなるため、開発期間・コストともに上昇

構成の柔軟性とコスト・納期のバランスを取る中間的な方式とも言えます。

Standard Cell(スタンダードセル)とは?

Standard Cell方式は、最適化されたセルライブラリ(論理ゲート・メモリ・アナログ回路など)を自由に配置・配線する構造です。

- ベーシックセルに縛られず設計できるため、集積度・性能ともに最も優れる

- その反面、下地・パッケージ・試験基板すべてを専用設計する必要があり、コストと開発期間は最も高くなります

3方式の比較まとめ

| 項目 | Gate Array | Embedded Array | Standard Cell |

|---|---|---|---|

| 下地の共有 | 可能 | 一部不可 | 不可(個別設計) |

| 設計自由度 | △(制限あり) | ○(マクロ追加可能) | ◎(自由度最大) |

| 開発期間 | ◎(短い) | △ | ×(長い) |

| 製造コスト | ◎(安い) | △ | ×(高い) |

| 集積度・性能 | △ | △ | ◎ |

最適な方式の選び方

- Gate Array:とにかく早く・安く

- Embedded Array:汎用性を取り入れつつもコストは抑えたい

- Standard Cell:性能最優先、製品寿命の長い製品向け

まとめ

「ASIC」と一言で言っても、構造ごとの特徴・向き不向きが大きく異なります。

設計者としては、コスト・納期・性能の要件に応じて、最適な構造方式を見極めることが大切です。

最新のテクノロジでは、集積度・性能が高くなりますのでStandard Cellが一般的です。

関連製品

- Socionext

- PGC

参考文献

更新履歴

2025/7/29 新規作成