こんにちは。レスター エンベデッド技術本部です。

今回は、ASICのプロセス技術とパッケージ技術のトレンドについて簡単にご紹介します。

ASICと周辺技術の基本を整理する

まずは用語の整理として、以下の分類を理解しておくことが重要です。

- ASIC(Application Specific Integrated Circuit):特定用途向けに設計された集積回路。CPUなどは通常含まれません。

- SoC(System on Chip):CPUコアなどを含めた複数機能をワンチップに集積した設計。コア入りASICとも言えます。

- ASSP(Application Specific Standard Product):汎用性を持たせた特定用途向けの標準製品です。

- FPGA(Field Programmable Gate Array):後から書き換え可能な柔軟なLSIです。

これらの分類は、開発におけるコスト、期間、柔軟性の最適なバランスを検討する上で、重要な視点となります。

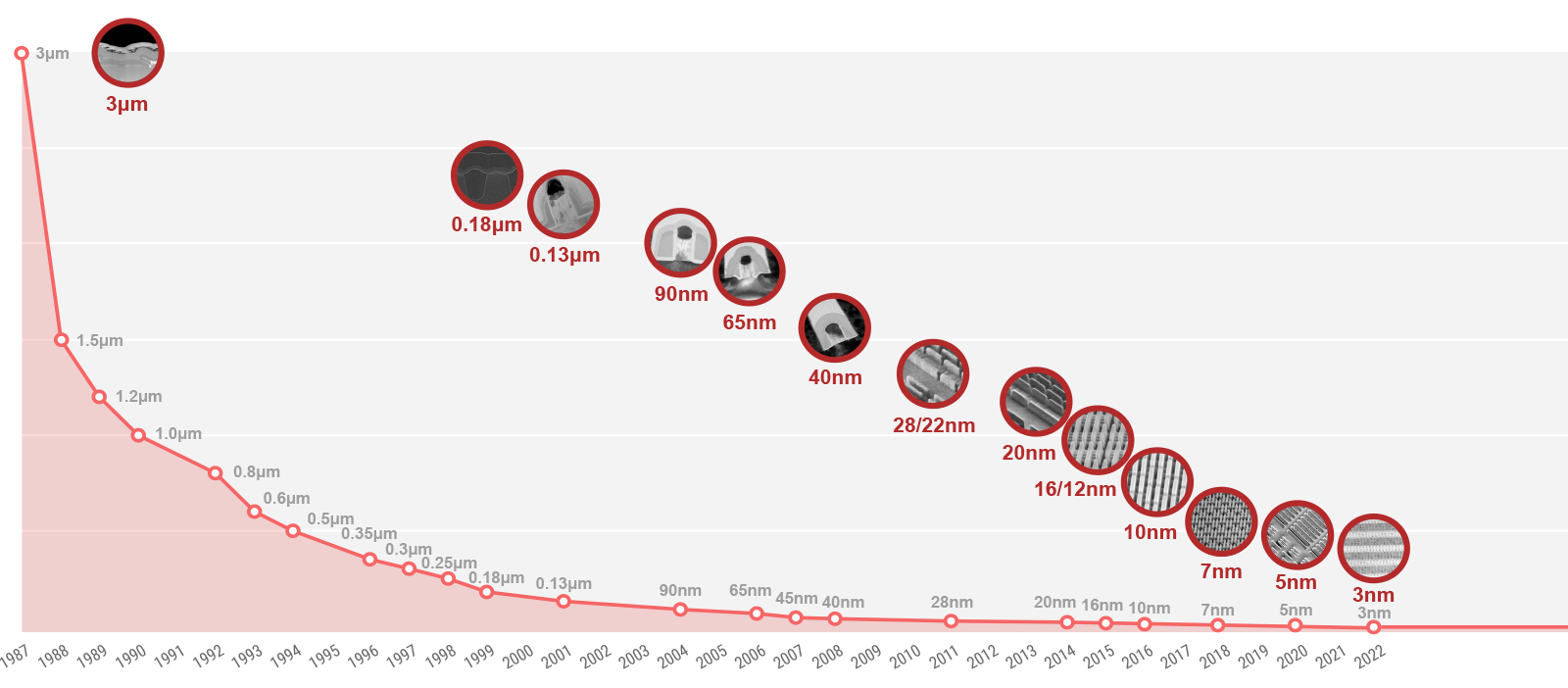

プロセスルールの進化

半導体における「プロセスルール(ノード)」とは、かつてはトランジスタのゲート長を意味していました。

10nm、7nm、5nm…といった具合です。

ところが現在は、「FinFET(3D構造のトランジスタ)」の登場でこの定義が曖昧になっています。

ムーアの法則と名称の変化

かつては「18か月で集積度が2倍になる」と言われたムーアの法則に従い、プロセスルールの数字で進化度を表現していましたが、現在は企業ごとにブランド的な命名が主流です。

- TSMC:N5、N3、N2、A16…

- Intel:Intel 4、Intel 3、Intel 20A など

FinFET構造では、もはやゲート長は「〇nm」の数値に対応しておらず、マーケティング名称に近い状態です。

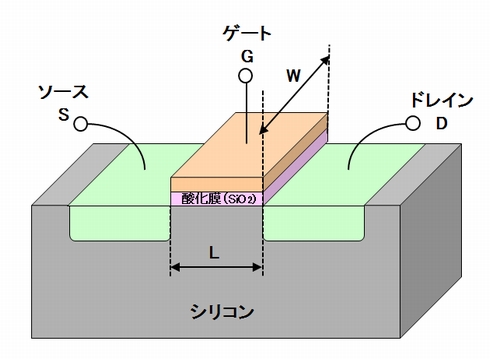

なぜ「nm」が意味を持たなくなったのか?

従来は、MOSトランジスタ断面の「ゲート長(L)」を指標としていました。

しかし、FinFET(立体構造トランジスタ)の登場により話は変わります。

FinFETは3D構造を持ち、もはや「ゲート長=プロセスノード」という単純な関係は崩壊。

Lの長さで性能や世代を語ることができなくなってきたのです。

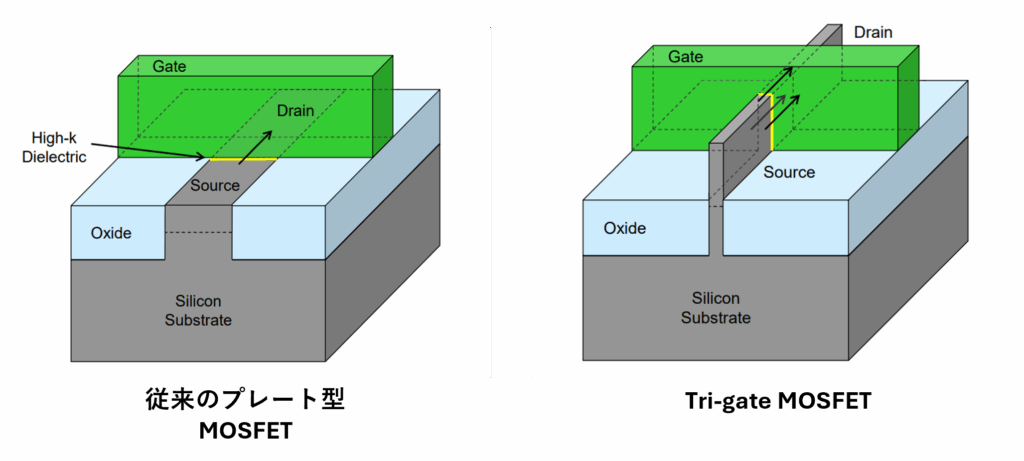

FinFET構造とは?

FinFETとは、フィン(魚のヒレ)状の立体的なチャンネルを持つトランジスタ構造のこと。

正式には「Tri-Gate型MOSFET」とも呼ばれ、3方向からゲート制御を行う仕組みです。

この構造によって、次のようなメリットが得られます。

- 漏れ電流の大幅な低減

- スイッチングの高速化

- 電力効率の向上

トランジスタの微細化が限界に近づく中で、FinFETのような3D構造が次のブレイクスルーとして、最先端の半導体設計を支えています。

パッケージ技術の進化

半導体の製造工程は、大きく分けて「前工程」と「後工程」に分類されます。

- 前工程:シリコンウェハ上にトランジスタや回路を作り込むフェーズ

- 後工程:完成したウェハを切り出し、外部と接続できるように“パッケージ化”するフェーズ

これまで注目されがちだったのは微細化が進む前工程ですが、実は今、後工程=パッケージ技術の革新が注目されています。

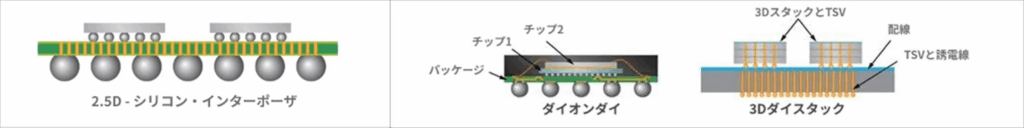

かつて主流だったQFPから始まり、BGA、多ピンCSP、Flip Chipなどを経て、現在は2.5D/3D実装が主流です。

実装スタイルの進化

パッケージ形状や接続方式も、大きく変化しています。

従来:

- QFP(Quad Flat Package):リード(足)が外に出た平面的パッケージ

- DIP(Dual In-line Package):基板に差し込むタイプ

現在:

- BGA(Ball Grid Array):裏面にボール状端子を並べて実装、配線密度向上

- CSP(Chip Scale Package):チップサイズと同じスケールの超小型パッケージ

- Flip Chip(フリップチップ):チップを裏返して直接バンプ接続、高速化と高密度実装が可能

そして未来:

- 3D実装:複数チップを垂直に積み重ね、基板面積を節約しつつ大規模化を実現

これにより、単なる「小型化」ではなく、高性能化と低消費電力の両立が可能になっています。

チップレットとは?

今注目されているのがチップレット技術です。

かつては1チップに集積するのが王道でしたが、最近は小さなチップを複数パッケージ内で組み合わせる方向に。

この技術は単なる微細化ではなく、「構造の最適化」による性能・コスト両立を実現する革新的アプローチです。

まとめ

ASICやパッケージ技術は今、「微細化だけではない多様な進化」が求められる時代に突入しています。

FinFETやチップレットといった技術が、設計や開発プロセス、果ては業界構造にも大きな変化をもたらしており、ハードウェア開発者にとって常にアップデートが欠かせない分野です。

本記事が、皆さんの技術理解や今後の設計方針のヒントになれば幸いです。

関連製品

- Socionext

- PGC

参考文献

更新履歴

2025/7/11 新規作成